#### DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### **1** Overview

DP3364S is a common anode 16-channel low turn PWM constant current driver chip designed for LED display, the chip integrates high-precision current generation circuit technology, so that the current error between the chips can be controlled within 2.0%, and integrates a variety of exclusive technology to improve the display effect of LED display, bring more improvement for the display effect.

#### 2 Features

- Power supply voltage range: 2.6 ~ 5.5V

- Operating temperature range: -40°C ~ 85°C

- Scanned area : 1 ~ 64 scans , arbitrarily adjustable

- 16 constant current output channels

- Support non-external resistor mode

- Constant current output range

- 0.5mA~18mA (V<sub>out</sub>=0.3V)

- $0.5 \text{mA} \sim 25 \text{mA}$  (V<sub>out</sub>=0.6V)

- Inter-channel current error

- Typical value: ±1.2% Max: ±2.0%

- Inter-chip current error

- Typical value: ±0.2% Max: ±2.0%

- Supports up to 128x frame rate

- High gray independent refresh, no inter-frame black field

- Optimize the display effect

- improve low gray uniformity

- improve the first line darkening

- improve up and down ghosting

- improve high-low gray coupling

- improve coupling of adjacent modules

- Internal Integration PLL produces internal GCLK with lower EMI

- Encapsulation mode: QSOP24/QFN24

#### **3** Application Fields

- High refresh rate LED video display

- LED full-color display

- High density and small pitch LED panel display

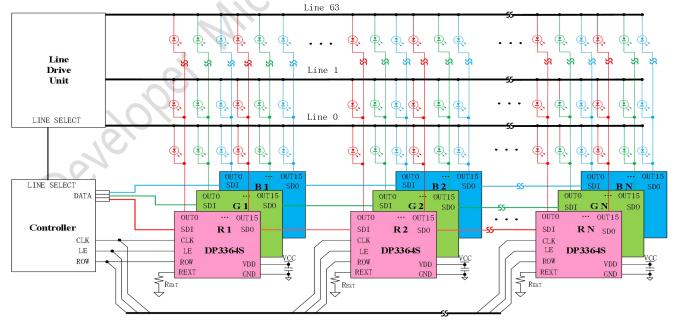

DP3364S Typical Application Schematic

www.depuw.com

DP3364S\_REV1.0\_EN

德晋微电子 DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### Content

| 1 Overview1                                                                    |

|--------------------------------------------------------------------------------|

| 2 Features1                                                                    |

| 3 Application Fields1                                                          |

| 4 Products Description4                                                        |

| 5 Electric schematic diagram5                                                  |

| 5.1 Input/Output Equivalent Circuit5                                           |

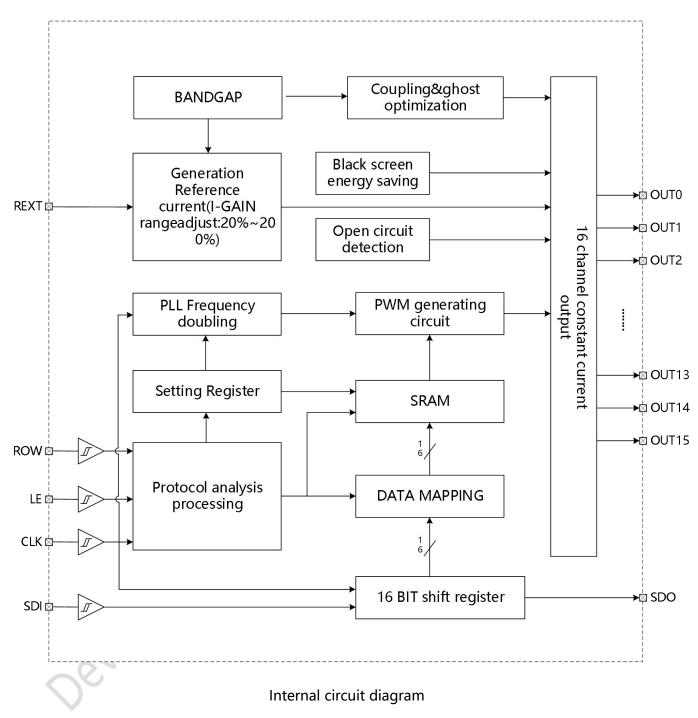

| 5.2 Internal Circuit Block Diagram6                                            |

| 6 Parameter List7                                                              |

| 6.1 Maximum Limit Parameter7                                                   |

| 6.2 Electrical Characteristics7                                                |

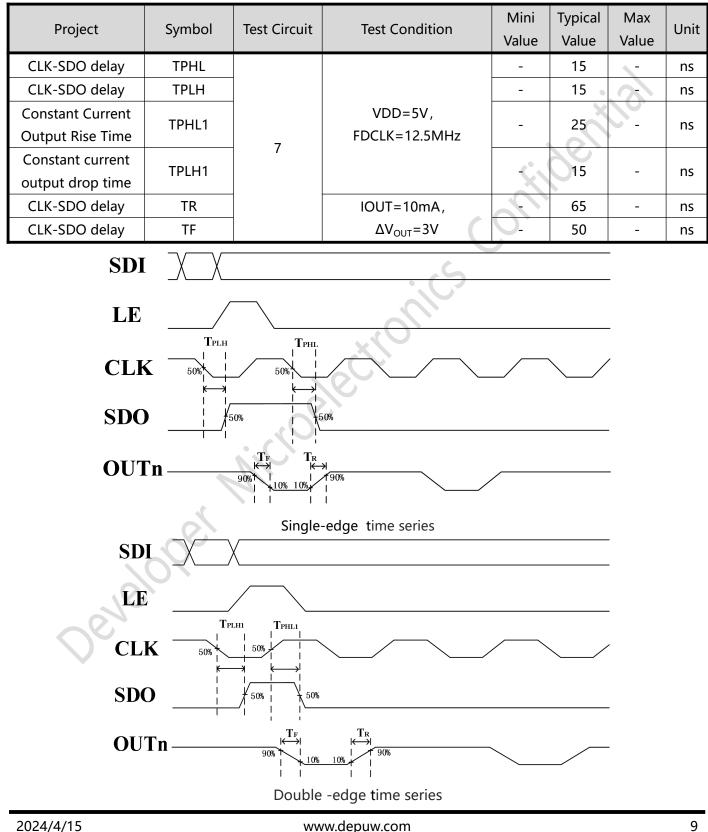

| 6.3 Dynamic Characteristics9                                                   |

| 7 Test Circuit Diagram 10                                                      |

| 7.1 Test Circuit 110                                                           |

| 7.2 Test Circuit 210                                                           |

| 7.3 Test Circuit 311                                                           |

| 7.4 Test Circuit 411                                                           |

| 7.5 Test Circuit 512                                                           |

| 7.6 Test Circuit 612                                                           |

| 7.7 Test Circuit 713                                                           |

| 8 Typical Characteristic Diagram13                                             |

| 8.1 Constant Current Source Inflection point13                                 |

| 8.2 Adjust Output Current by An External Resistance. 14                        |

| 8.3 Current Gain without External Resistance mode,adjust current with register |

| 9 Typical Display Effect Image15                                               |

| 9.1 Display Effect15                                                           |

| 9.1.1 Remove Open Circuit Bad Spot Crosses                                     |

| 9.1.2 Remove Ghosting and coupling Effects                                     |

| 9.1.3 High and low gray interference and coupling display bad effect optimization |          |

|-----------------------------------------------------------------------------------|----------|

| 10 Instruction and Register                                                       |          |

| 10.1 Register Instruction                                                         | .18      |

| 10.2 Data Instructions                                                            | .18      |

| 10.3 Single/Double Mode Switch                                                    | .18      |

| 10.4 Write Register                                                               | 20       |

| 10.5 Register Signal Sending Way                                                  | 20       |

| 10.6 ROW Signal Sending Way                                                       | 20       |

| 10.7 PWM Display Mode                                                             | . 21     |

| 10.7.1 General Frame Synchronization Mode                                         | .22      |

| High Gray Data Refresh Frame Synchroni                                            | zation M |

|                                                                                   | 22       |

| 10.7.3 High-gray data Independently Refreshes                                     |          |

| Asynchronous Mode                                                                 | .22      |

| 10.7.4 low gray and high brush mode                                               | .23      |

| 10.8 Relevant Configuration of PWM Display                                        | 23       |

| 10.8.1 Number of Row Scans Configured                                             | . 23     |

| 10.8.2 Row Grayscale Configuration                                                | 23       |

| 10.8.3 PWM Display Packet Configuration                                           | 23       |

| 10.8.4 Internal Grayscale Clock Configuration                                     | 24       |

| 10.8.5 PWM Gray scales Series & Gamma Generati                                    | ion24    |

| 10.9 Open Circuit Detection and Removal of Bad Spc                                | ots24    |

| 11 Package cooling power( $P_D$ )                                                 | 24       |

| 12 Load Terminal Voltage(VLED)                                                    | . 25     |

| 13 Encapsulation Information                                                      | .26      |

| l4 Important statement错误!未定义书签                                                    | 5.0      |

www.depuw.com

#### **DP3364S**

16 通道 PWM 恒流驱动

#### Declaration

| Version | Date    | Reviser  | Revised Contents |

|---------|---------|----------|------------------|

| V1.0    | 2024.04 | Wang Mei | Original Version |

#### **4** Products Description

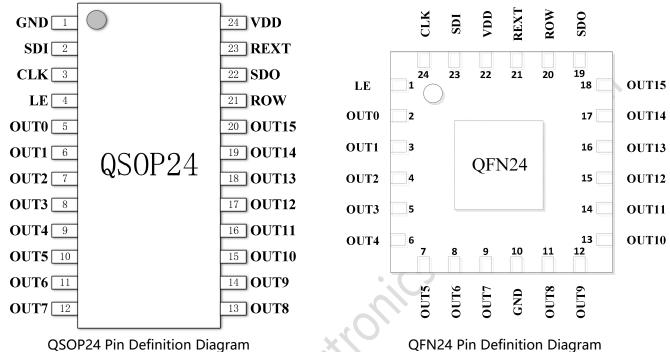

**Pin Definition**

QSOP24 Pin Definition Diagram

**Pin Description**

| QSOP24 Pin No. | QFN24 Pin NO. | Pin Name   | Pin Description                                                                    |

|----------------|---------------|------------|------------------------------------------------------------------------------------|

| 1              | 10            | GND        | Chip Grounding Terminal                                                            |

| 2              | 23            | SDI        | Serial Data Input Terminal                                                         |

| 3              | 24            | CLK        | Serial Clock Input                                                                 |

| 4              | 1             | LE         | Data and Instruction Latch , different LE length represents different instructions |

| 5~20           | 2~9 11~18     | OUT0~OUT15 | Constant Current Output Terminal                                                   |

| 21             | 20            | ROW        | Row Switching Signal                                                               |

| 22             | 19            | SDO        | Serial Data Output                                                                 |

| 23             | 21            | REXT       | Connect the External Resistance Terminal                                           |

| 24             | 22            | VDD        | POWER END                                                                          |

www.depuw.com

**協普微电子** DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

• Product Purchase Information

| Product Name | Encapsulation mode | Packing Method | Quantity/Disc | Humidity Level |

|--------------|--------------------|----------------|---------------|----------------|

|              | QSOP24             | Таре           |               |                |

| DP3364S      | QFN24              | Таре           | 5000          | MSL=3          |

Product Marking

QSOP24

DP3364S XXXXXXXX QFN24

DP3364S is the product name. XXXXXX represents the product batch number.

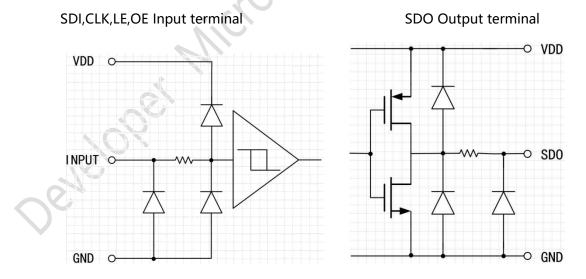

#### 5 Electric schematic diagram

#### 5.1 Input/Output Equivalent Circuit

www.depuw.com

DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### 5.2 Internal Circuit Block Diagram

www.depuw.com

6

DP3364S

德省 微 电子

DP3364S

DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### 6 Parameter List

#### 6.1 Maximum Limit Parameter

| Project                  | Symbol           | Rated Value                 | Unit |

|--------------------------|------------------|-----------------------------|------|

| Supply Voltage           | V <sub>DD</sub>  | 0 ~ 6                       | V    |

| Output Current           | Ι <sub>ο</sub>   | 25                          | mA   |

| Input Voltage            | V <sub>IN</sub>  | -0.4 ~ V <sub>DD</sub> +0.4 | v    |

| Output withstand voltage | V <sub>OUT</sub> | 11                          | V    |

| Clock frequency          | F <sub>CLK</sub> | 25                          | MHz  |

| Operating Temperature    | T <sub>opr</sub> | -40 ~ 85                    | °C   |

| Storage Temperature      | T <sub>stg</sub> | -55 ~ 150                   | °C   |

• All voltage values are based on the chip grounding terminal (GND) as a reference point, and the test temperature for the maximum limit parameter is 25°C.

- If the actual working conditions exceed the specified value may cause permanent damage to the components; If the actual operating conditions are slightly below the maximum and work for a long time, the reliability of the component may be reduced. The above values are only partially specified, and this product does not support functional operation under other conditions outside the specifications.

- The maximum peak welding temperature of surface paste products shall not exceed 260°C. The temperature curve shall be set by the factory according to J-STD-020 standard, the actual situation of the factory and the solder paste manufacturer's suggestion.

### 6.2 Electrical Characteristics

(Unless otherwise specified,  $VDD=3.5V \sim 5V$ ,  $Ta=25^{\circ}C$ )

| Project                            | Symbol                                                           | Test<br>Circuit                                                    | Test Cor                                                                    | ndition               | Mini<br>Value | Typical<br>Value | Max<br>Value | Unit |

|------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|---------------|------------------|--------------|------|

|                                    | VR_TT                                                            |                                                                    | V <sub>DD</sub> =5V,R <sub>EXT</sub> =1K<br>IGAIN=100%,T <sub>a</sub> =25°C |                       | -             | 1.484            | -            | v    |

| REXT voltage                       | VR_LT                                                            |                                                                    | V <sub>DD</sub> =5V<br>R <sub>EXT</sub> =1K                                 | T <sub>a</sub> =-40°C | -             | 1.468            | -            | V    |

| characteristics                    | characteristics VR_HT I IGAIN=100%<br>VR_LV T <sub>a</sub> =25°C | VR_HT         I         IGAIN=100%           VR_LV         Ta=25°C | T <sub>a</sub> =85°C                                                        | -                     | 1.492         | -                | V            |      |

|                                    |                                                                  |                                                                    | $V_{DD}$ =5.5V                                                              | -                     | 1.487         | -                | V            |      |

|                                    | VR_HV                                                            |                                                                    | R <sub>EXT</sub> =1K<br>IGAIN=100%                                          | V <sub>DD</sub> =2.6V | -             | 1.494            | -            | v    |

| Constant current output inflection | V <sub>OUT1</sub>                                                | 2                                                                  | V <sub>DD</sub> =5.0V<br>R <sub>EXT</sub> =1k                               | IOUT=18m<br>A         | -             | 350              | -            | mV   |

| point                              | V <sub>OUT2</sub>                                                |                                                                    | Inflection                                                                  | IOUT=9mA              | -             | 290              | -            | mV   |

2024/4/15 DP3364S REV1.0 EN www.depuw.com

8

德普微电子 DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

|                                   |               | V <sub>OUT3</sub>  |   | point level 0                      | IOUT=4.5m<br>A | -                   | 260   | -               | mV  |

|-----------------------------------|---------------|--------------------|---|------------------------------------|----------------|---------------------|-------|-----------------|-----|

|                                   |               | V <sub>OUT4</sub>  |   | V <sub>DD</sub> =5.0V              | IOUT=18m<br>A  | -                   | 460   | -               | mV  |

|                                   |               | V <sub>OUT5</sub>  |   | R <sub>EXT</sub> =1k<br>inflection | IOUT=9mA       | -                   | 390   | -               | mV  |

|                                   |               | V <sub>OUT6</sub>  |   | point level 1                      | IOUT=4.5m<br>A | -                   | 360   | -               | mV  |

| Constant c                        | urrent        | IOUT               |   | inflection po                      | oint level 0   | 0.5                 | -     | 18              | mA  |

| source ou<br>range                | •             | IOUT1              | 2 | inflection po                      | pint level 1   | 0.5                 | - ~   | 25              | mA  |

| Constant c<br>source ou<br>range  | itput         | DCHIP              | 2 | VDS=                               | 0.6V           | -<                  | ±1.5  | ± 2.0           | %   |

| Inter-chip c<br>current e         | -             | DCHL               | 2 | VDS=0.6V                           |                | G,                  | ± 1.2 | ±2.5            | %   |

| Output cu<br>error betv<br>channe | veen          | %/Δ <sub>VDS</sub> | 2 | VDS=0.3~3.0V                       |                | _                   | _     | ± 1.0           | %/V |

| Constant c<br>error/VDS va        |               | %∕∆ <sub>vdd</sub> | 2 | VDD=3.5V~5.0V                      |                | —                   | _     | ± 1.0           | %/V |

| output volt<br>ON                 | age at        | V <sub>O(ON)</sub> | 2 | OUT0~OUT15                         |                | 0.3                 | -     | V <sub>DD</sub> | V   |

| SDO drive                         | High<br>Level | ЮН                 | 3 | VDD                                |                |                     | -22   | _               | mA  |

| current                           | Low<br>Level  | IOL                | 5 |                                    | VDD=5V         |                     | 23    | _               | mA  |

| Output                            | High<br>Level | VOH                |   | IOH=-                              | 1mA            | 4.6                 | —     | _               | V   |

| Level                             | Low<br>Level  | VOL                | 4 | IOL=1                              | ImA            | _                   | —     | 0.4             | V   |

| SDO drive                         | High<br>Level | VIH                | F | -                                  |                | 0.7*V <sub>DD</sub> | -     | V <sub>DD</sub> | V   |

| current                           | Low<br>Level  | V <sub>IL</sub>    | 5 | -                                  |                | GND                 | -     | 0.3*V           | V   |

www.depuw.com

DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### 6.3 Dynamic Characteristics

(Unless otherwise specified,  $VDD=3.5V \sim 5V$ , Ta=25°C)

DP3364S REV1.0 EN

www.depuw.com

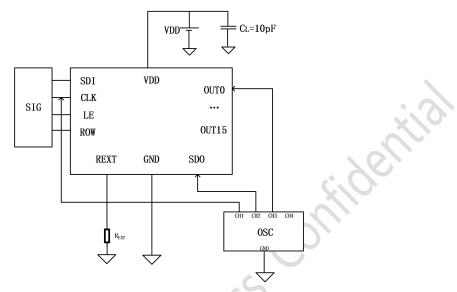

#### **Test Circuit Diagram** 7

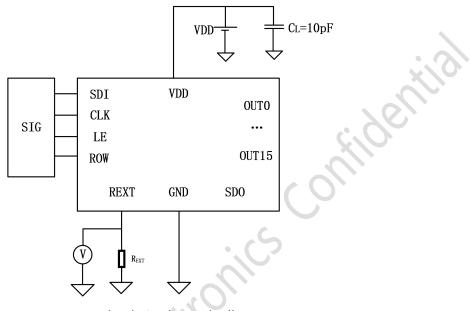

#### 7.1 Test Circuit 1

External resistance voltage

Test circuit 1 schematic diagram

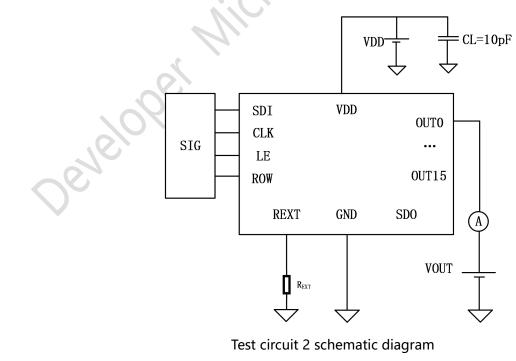

#### 7.2 Test Circuit 2

Constant current output inflection point voltage & corresponding inflection point current (under open circuit detection)

www.depuw.com

德音微电子 DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

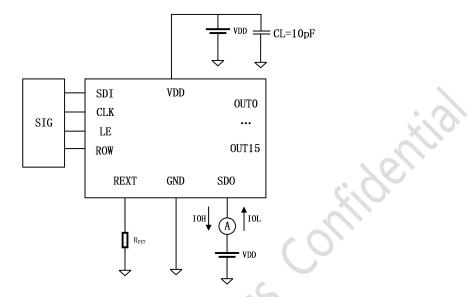

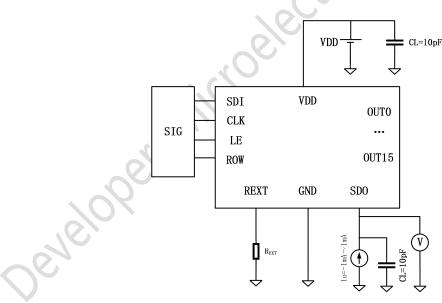

#### 7.3 Test Circuit 3

• IOH、IOL

Test circuit 3 schematic diagram

• VOH、VOL

Test circuit 4 schematic diagram

www.depuw.com

## DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

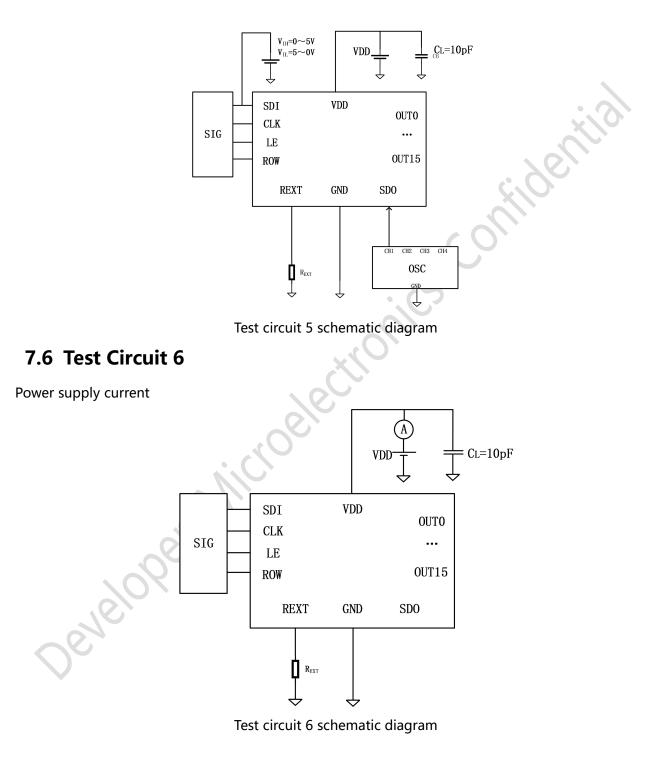

#### 7.5 Test Circuit 5

• VIH、VIL

www.depuw.com

(

信 御 宅 子

DP3364S

DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### 7.7 Test Circuit 7

• Dynamic Characteristic

Test circuit 7 schematic diagram

#### 8 Typical Characteristic Diagram

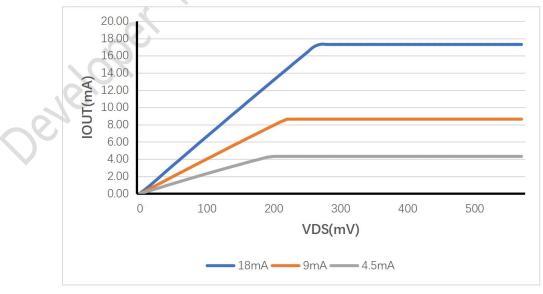

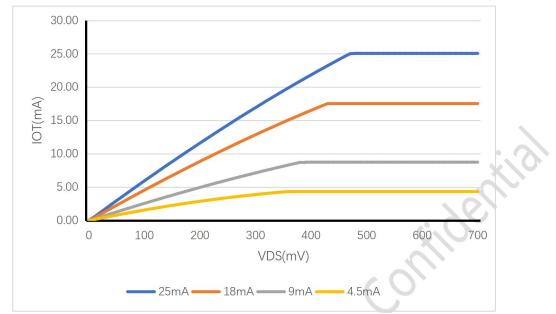

#### 8.1 Constant Current Source Inflection point

When the DP3364S is applied to LED displays, Chip-Chip Skew and channel skew is minimal ,it is due to the DP3364S having excellent constant current output characteristics:

- The maximum channel current error on-chip is less than ±2.5%, and the maximum inter- chip current error is less than ±2.0%;

- When the load terminal voltage (V-out) changes, the stability of the output current is not affected, as shown in the figure below:

2024/4/15 DP3364S REV1.0 EN www.depuw.com

DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

DP3364S

Low inflection Point mode and VDD=2.6~5V, relationship curve between  $I_{OUT}$  and  $V_{OUT}$

Non- Low inflection Point mode and VDD= $2.6 \sim 5V$ ,  $I_{OUT}$  and  $V_{OUT}$  relationship curve

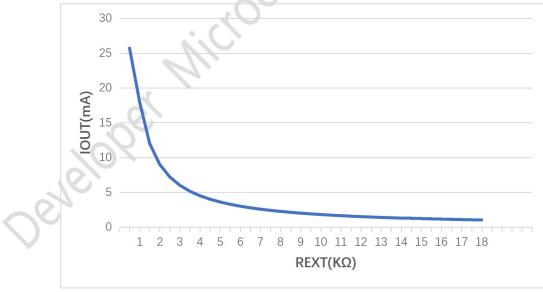

#### 8.2 Adjust Output Current by An External Resistance

Output current value is calculated by the following formula:

$$IOUT = \frac{IGAIN*18}{Rext}, 20\% \le IGAIN \le 200\%$$

The REXT in the formula is the resistance value between ground and the chip's 23PIN port. For example, when the current gain IGAIN=100%, REXT=1k $\Omega$ , the formula works out the I<sub>OUT</sub> value 18mA.

IGAIN=100%, the relationship between REXT and lout

www.depuw.com

#### 8.3 Current Gain without External Resistance mode, adjust current

#### with register

The output current value is calculated by the following formula:

$I_{out} = [70uA + 0.4uA^{*}(reg0x0f < 6:0 > -16)]^{*}reg0x08 < 7:0 > ^{(1+0.5*reg0x0b < 5>)}$

#### 9 Typical Display Effect Image

• The specific display effect will be affected by the conditions of the lamp board and register parameters. The following test results are for reference only.

#### 9.1 Display Effect

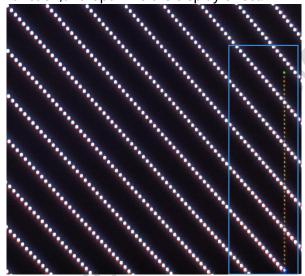

#### 9.1.1 Remove Open Circuit Bad Spot Crosses

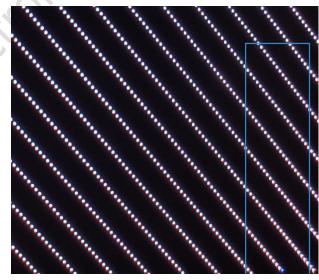

The following is a comparison of the display effect before and after removing the open circuit bad spot cross, you can see:

Chip can remove the bad cross well after opening the function removing the open bad cross function, and optimize the display effect.

Display Effect before Removing open circuit bad spots cross

Display effect after removing the open circuit bad spot cross

www.depuw.com

#### 9.1.2 Remove Ghosting and coupling Effects

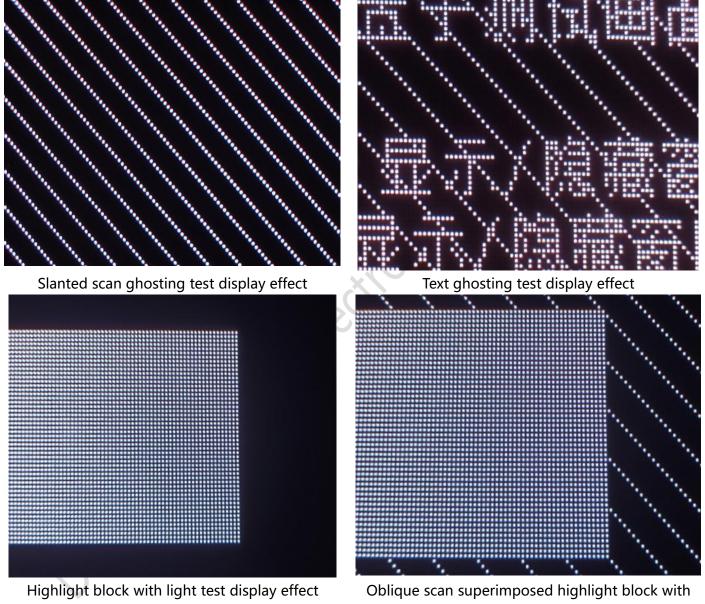

Below is the removal of ghosting and no band lighting effect, you can see:

- Oblique scanning ghost, text ghost and other problems cannot be observed.

- Highlight block with bright, oblique scan superimposed highlight block with bright test results are very good.

- Chip shows good display effect.

light test display effect

www.depuw.com

### 9.1.3 High and low gray interference and coupling display bad

#### effect optimization

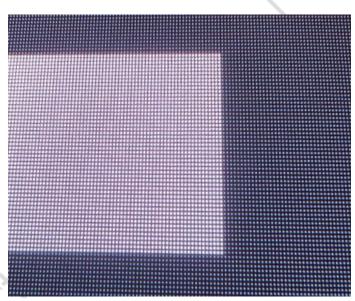

The following figure is the optimization effect of high-low gray interference and coupling display poor effects, you can see:

- The low gray coupling of the black block and the low gray coupling of the white block are not sensed.

- Chip shows good display effect.

Black block on the low gray ,coupling test effect

White block on the low gray, coupling test effect

www.depuw.com

德音微电子 DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### **10 Instruction and Register**

#### **10.1 Register Instruction**

| Instruction Name | LE | Description              |   |

|------------------|----|--------------------------|---|

| DATA_LATCH       | 1  | Latch 16bit data to SRAM |   |

| VSYNC            | 3  | Update Display Data      |   |

| WR_CFG           | 5  | Write Register           |   |

| PRE_ACT          | 14 | Write Enable             | K |

| DDR              | 2  | Enter Double-edge Mode   |   |

| SDR              | 15 | Enter Single-edge Mode   |   |

#### **10.2 Data Instructions**

| Data sending<br>Sequence | Line    | Channel            |

|--------------------------|---------|--------------------|

| 1                        | Line 0  | Channel 15 (OUT15) |

| 2                        |         | Channel 14 (OUT14) |

|                          |         |                    |

| 16                       | 5       | Channel 0 (OUT0)   |

| 17                       | Line 1  | Channel 15 (OUT15) |

| 18                       |         | Channel 14 (OUT14) |

|                          |         |                    |

| 32                       |         | Channel 0 (OUT0)   |

|                          |         |                    |

| 1009                     | Line 63 | Channel 15 (OUT15) |

| 1010                     |         | Channel 14 (OUT14) |

|                          |         |                    |

| 1024                     |         | Channel 0 (OUT0)   |

#### **10.3 Single/Double Mode Switch**

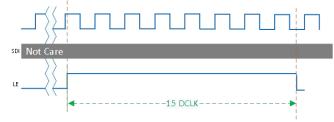

1.Data are collected at the rising edge of the CLK signal in single edge mode; Data are collected at the rising&falling edge of the CLK signal in Double edge mode.

2. CLK rising edge counting is used for fixed OE signal width.

3. The command for single-mode and dual-mode along mode switchover needs to be sent once after it is powered on.

4.Need to enter the single edge mode after power-on, send the command shown in the following figure.

www.depuw.com

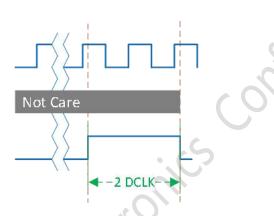

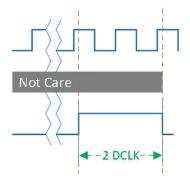

SDR15 DCLK edges (up + down) are set to SDR

★ IF need to enter the double-edge mode after power-on, You need to send the commands shown in the image below:

The two DCLK rising edges are set to DDR

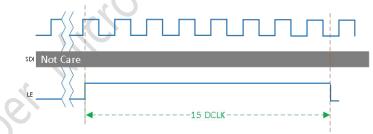

USER want to switch single -edge mode /double-edge mode when debug, operation is as follows: If you are already in double-edge mode and need to enter single-edge mode, sending the following command.

In double edge mode, 15 DCLK edges (up + down) are set to SDR If already in single edge mode, you need to enter double edge mode

In single-edge mode, the two DCLK rising edges are set to DDR

2024/4/15 DP3364S REV1.0 EN www.depuw.com

## DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

#### **10.4 Write Register**

Send PRE ACT first, then run WR CFG, LE is 5 DCLK width, the first input 8bit is the register address bit, the last input 8bit is the data bit of the corresponding register address.

For example:

{A7, A6, A5, A4, A3, A2, A1, A0} = 8' b0000 0111;

{D7, D6, D5, D4, D3, D2, D1, D0}=8' b1001 1101;

That is, register 0x07 (8 'b0000 0111) is set to 8' b1001 1101.

#### **10.5 Register Signal Sending Way**

The specific driving methods are as follows:

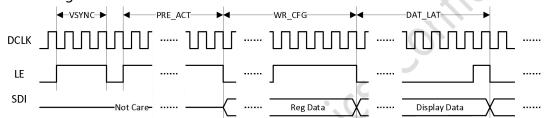

As shown in the figure above, the order of sending instructions and data in each frame:

- 1. Send VSYNC.

- 2. Send PRE ACT.

- 3. Send WR CFG and write the register configuration. Each frame can only write a register value of one address, and 15 frames complete the refresh of all registers (a total of 15 valid register addresses) to save configuration time.

- 4. Send DAT LAT several times to write display data with SDI.

- 5. The data sending bit is displayed as 16 bits.

#### **10.6 ROW Signal Sending Way**

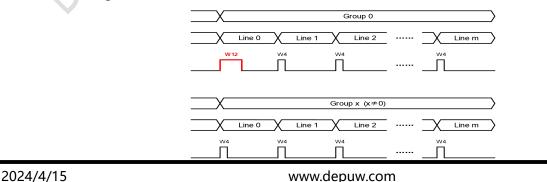

The DP3364S integrated on-chip GCLK generation circuit changes the OE signal of the universal constant current chip to the ROW signal, using the ROW.

The rising edge of the ROW represents the beginning of a row display, where the high level width of the ROW has two types, namely:

1.W12: The high-level width of the ROW is 12 DCLK width

2.W4: The high-level width of the ROW is 4 DCLK width

DP3364S REV1.0 EN

www.depuw.com

20

As shown in the figure above, when ROW signals are sent, only the first ROW of Group 1 (Line 0) needs to send ROW signals of W12, and other ROW signals are sent according to W4.

#### **10.7 PWM Display Mode**

DP3364S integrated four PWM display modes:

- 1. General frame synchronization mode; 2. High-gray data independent refresh synchronous mode;

- 3. High-gray data independently refreshes asynchronous mode; 4. Low Ash High Brush mode .

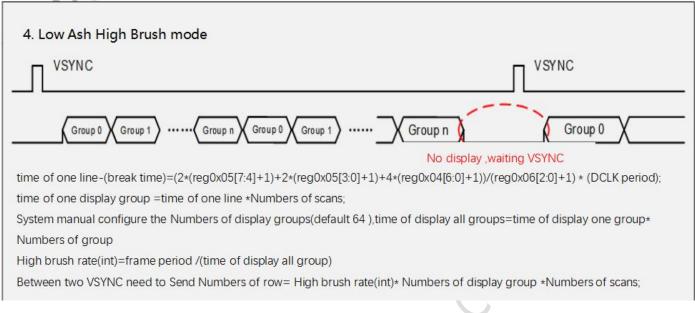

| 1.General frame synchronization mode                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                      |

| Group 0 X Group 1 X Group 2 X X Group n Group 0 X                                                                                                                    |

| System automatically configure the Numbers of display groups; No display ,waiting VSYNC                                                                              |

| Numbers of display groups(int) =frame period /time of one display group;                                                                                             |

| time of one display group =time of one line *Numbers of scans;                                                                                                       |

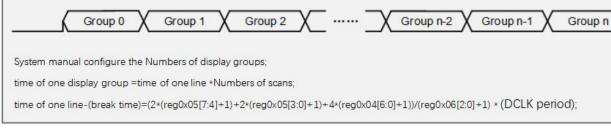

| time of one line-(break time)=(2*(reg0x05[7:4]+1)+2*(reg0x05[3:0]+1)+4*(reg0x04[6:0]+1))/(reg0x06[2:0]+1) * (DCLK period);                                           |

|                                                                                                                                                                      |

| 2. High-gray data independent refresh synchronous mode       VSYNC       Group 0       Group 0       Group 1       Group 1       Group 0       Group 0       Group 1 |

| System automatically configure the Numbers of display groups;                                                                                                        |

| Numbers of display groups(int) =frame period /time of one display group;                                                                                             |

| time of one display group =time of one line *Numbers of scans;                                                                                                       |

| time of one line-(break time)=(2*(req0x05[7:4]+1)+2*(req0x05[3:0]+1)+4*(req0x04[6:0]+1))/(req0x06[2:0]+1) * (DCLK period);                                           |

|                                                                                                                                                                      |

|                                                                                                                                                                      |

| 3. High-gray data independently refreshes asynchronous mode                                                                                                          |

2024/4/15

#### www.depuw.com

Group 0

DP3364S\_REV1.0\_EN

DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

DP3364S

#### 10.7.1 General Frame Synchronization Mode

Working mode and related configurations as follow:

- 1. Configure REG0X0C [7:6] = 0 and set the PWM display mode to Universal Frame Sync Mode

- 2. The number of DCLK per line is calculated using the Formula

- 3. The configuration shows the number of data sets, REG0X03[6:0] = refresh rate/frame rate -1

- 4. After VSYNC, display the first Line (Line 0) of Group 1(Group 0)

- 5. Stop displaying data from the current frame until the next VSYNC comes

#### 10.7.2 High Gray Data Refresh Frame Synchronization Model

#### Independently

Working mode and related configuration:

- 1. Set the PWM display mode to the high gray data independent refresh frame synchronization mode

- 2. Calculate a set of display time = frame cycle/(refresh rate/frame rate)

- 3. Calculate the display time of a row = a group of display time/the number of rows

4. The number of DCLK in each row is calculated according to the formula, which is met by adjusting the gray level of the row, DCLK frequency and register reg0x06[1:0]

5.ROW is continuously transmitted at a fixed display frequency without interruption. The frequency of the ROW is independent of VSYNC. The frequency of the ROW signal = the display time of 1/ROW = the time between the rising edges of 1/row

6. ROW 0 of group 0 sends ROW signals of W12. In other cases, ROW signals of W4 are sent. Each row signal (number of groups x number of row scans) contains only one W12.

#### 10.7.3 High-gray data Independently Refreshes Asynchronous Mode

Working mode and related configuration:

1. Set the PWM display mode to the asynchronous mode of high gray data independent refresh

www.depuw.com

DP3364S\_REV1.0\_EN

# **協 音 微 电子**DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

2. The number of DCLKS in each row is calculated according to the formula;

Display the number of data groups manually. The default value is 64 groups (reg0x03[6:0]=7 'h3f);

- 3. ROW is continuously transmitted at a fixed display frequency without interruption. The ROW frequency is independent of VSYNC. ROW signal frequency = 1/display time of ROW = 1/Time between rising edges of row;

- 4. ROW 0 of group 0 sends ROW signals of W12, and ROW signals of W4 are sent in other cases. Each row signal (number of groups (according to register configuration value) \* number of row scans) has only one W12, and it keeps cycling in this way.

- 5. Visual refresh rate=1/(time of display one line\*Numbers of scans).

#### 10.7.4 low gray and high brush mode

Working mode and related configuration:

- 1. Set PWM display mode to low gray and high brush mode

- 2. The number of groups displayed is manually configured (the default is 64 groups).

- 3. The numbers of DCLK is calculated according to the formula, and calculated the display time of a row ;

- 4. Calculate one group display time = a row display time \*scans

- 5. Calculate all group display time = one group display time \* Number of groups,

- 6. High brush rate (int) = frame cycle/display time of all groups

7. Two VSYNC need to send Numbers of ROW signal= high brush rate \* number of display groups \* scans

8. Display Line 1 (Line 0) of Group 1 (Group 0) after VSYNC

9. The current frame data display high brush rate after the display stops until the arrival of the next VSYNC

10. Visual refresh rate = frame rate \* number s of group \* High brush rate=(3840/7680)\*high brush rate 11. The low gray and high brush mode only needs to change the ROW signal according to the above steps, and the gray level does not need to be adjusted

### 10.8 Relevant Configuration of PWM Display

#### 10.8.1 Number of Row Scans Configured

DP3364S supports up to 64 line scans;

#### 10.8.2 Row Grayscale Configuration

reg0x04[6:0] represents the PWM display length of a row, the PWM display length of a row = reg0x04[6:0]+1, the maximum support line gray level 32X4=128

#### 10.8.3 PWM Display Packet Configuration

reg0x03[6:0] indicates the number of PWM display packets. The number of PWM display packets = reg0x03[6:0]+1. The maximum number of supported packets is 128;

In frame synchronization mode, PWM displays the number of packets = refresh rate/frame rate;configure reg0x03[6:0]-1

| 2024/4/15 |   |

|-----------|---|

|           | ^ |

www.depuw.com

DP3364S\_REV1.0\_EN

In asynchronous mode, PWM display packets can be configured independently (independent of refresh rate);

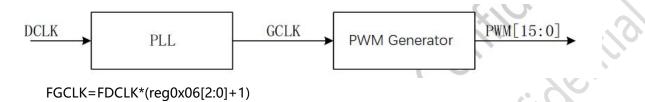

#### **10.8.4** Internal Grayscale Clock Configuration

DP3364S integrates PLL on chip to produce gray clock GCLK. The relevant calculation formula is as follows:

#### 10.8.5 PWM Gray scales Series & Gamma Generation

PWM gray level (maximum)= Line gray level \*PWM display group

Gamma can be calculated and generated according to the PWM gray level (maximum) (this part is generated by the control card manufacturer according to their own gamma generation formula)

The maximum chip gray level supports only 14bit.

#### 10.9 Open Circuit Detection and Removal of Bad Spots

Selected [Remove bad spots] : reg0x0c[1]=1 ;

Non-selected [Remove bad spots] : reg0x0c[1]=0

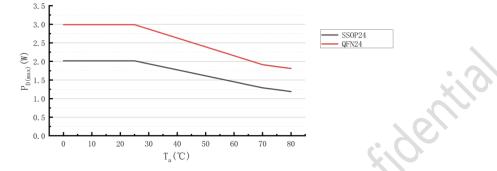

#### 11 Package cooling power(P<sub>D</sub>)

The maximum heat dissipation power of the encapsulation is determined by the formula:  $P_{D(\max)} = \frac{(T_j - T_a)}{R_{th(j-a)}}$

When all 16 channels are open, the actual power is:  $P_{D(act)} = I_{DD} * V_{DD} + I_{OUT} * Duty * V_{DS} * 16$

To ensure that  $P_{D(act)} \leq P_{D(max)}$  output maximum current and duty cycle relationship is:

$$I_{OUT (max)} = \frac{\frac{T_j - T_a}{R_{th(j-a)}} - (I_{DD} * V_{DD})}{V_{DS} * Duty * 16}$$

Therein T<sub>j</sub> is the junction temperature ( $T_j$ =150 °C) ,  $T_a$  is the ambient temperature ,  $V_{DS}$  is the constant current output port voltage , Duty is the duty cycle , and  $R_{th(j-a)}$  is the thermal resistance of the encapsulation.

2024/4/15 DP3364S REV1.0 EN www.depuw.com

DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

| encapsulation | R <sub>th(j-a)</sub> (°C/W) | P <sub>D(max)</sub> (W) |

|---------------|-----------------------------|-------------------------|

| QSOP24        | 62                          | 2.01                    |

| QFN24         | 41.8                        | 2.99                    |

|               |                             |                         |

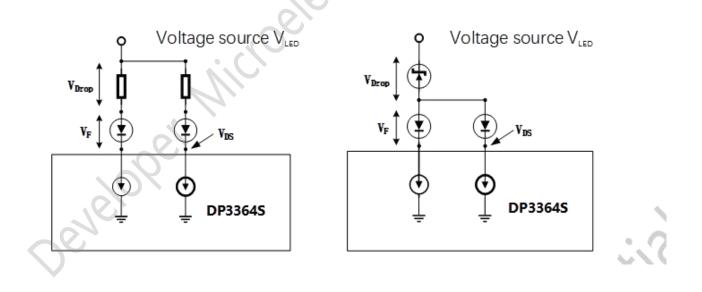

#### 12 Load Terminal Voltage(VLED)

德晋微电子

In order to optimize the heat dissipation capacity of the package, it is recommended that the best operating range of the output terminal voltage ( $V_{DS}$ ) is 0.3V to 1.0V( $I_{OUT}$ = 0.5-36mA). If  $V_{DS}$ = $V_{LED}$ -VF and  $V_{LED}$ =5V, the high output voltage ( $V_{DS}$ ) may cause PD (act) > PD (max); In this case, it is recommended to use the lowest possible  $V_{LED}$  voltage for use, and an external resistor or voltage regulator can also be used as a VDROP. This results in VDS=( $V_{LED}$ -VF)- $V_{DROP}$ , which reduces the input voltage ( $V_{DS}$ ) value. The application diagram of the external series resistor or voltage regulator can be referred to the following figure.

www.depuw.com

DP3364S

德晋微电子 DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

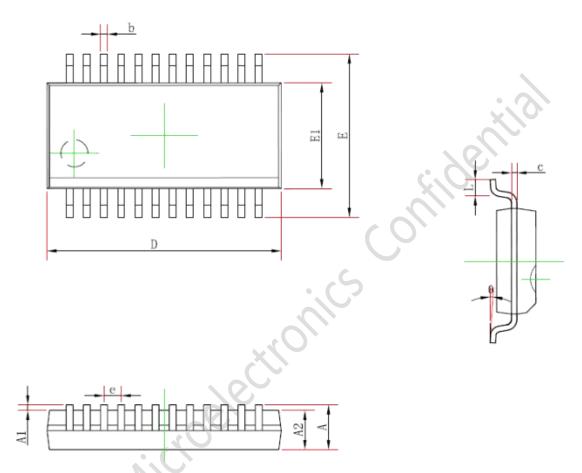

#### **13 Encapsulation Information**

QSOP24 Plastic Encapsulation Specification Drawing

|    | Millimeters (mm) |       |

|----|------------------|-------|

|    | Min              | Мах   |

| Α  |                  | 1.95  |

| A1 | 0.05             | 0.35  |

| A2 | 1.05             |       |

| b  | 0.1              | 0.4   |

| С  | 0.05             | 0.254 |

| D  | 8.2              | 9.2   |

| E1 | 3.6              | 4.2   |

| E  | 5.6              | 6.5   |

| е  | 0.635TYP         |       |

| L  | 0.3              | 1.5   |

| θ  | 0°               | 10°   |

www.depuw.com

德晋微电子 DP3364S DP3364S 16 Channel 64 scans Low-turning PWM Constant Current Driver

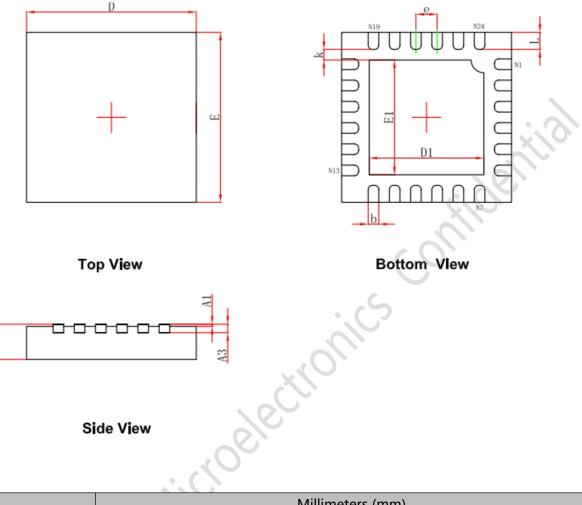

QFN24 Plastic Encapsulation Specification Drawing

|    | Millimeters (mm) |             |  |

|----|------------------|-------------|--|

|    | Min              | Max         |  |

| A  | 0.700/0.800      | 0.800/0.900 |  |

| A1 | 0.000            | 0.050       |  |

| A3 | 0.203REF         |             |  |

| D  | 3.924            | 4.076       |  |

| E  | 3.924            | 4.076       |  |

| D1 | 2.6              | 2.8         |  |

| E1 | 2.6              | 2.8         |  |

| k  | 0.20MIN          |             |  |

| b  | 0.200            | 0.300       |  |

| e  | 0.500TYP         |             |  |

| L  | 0.324            | 0.476       |  |

www.depuw.com

#### **14 Official Announcement**

Division I will ensure the accuracy and reliability of the product specification document, but we reserve the right to independently modify the content of the specification document without prior notice to the customer. Before placing an order, customers should contact us to obtain the latest relevant information and verify that this information is complete and up-to-date. All product sales are subject to the sales terms and conditions provided by our company at the time of order confirmation.

Division I will periodically update the content of this document. Actual product parameters may vary due to differences in models or other factors. This document does not serve as any express or implied guarantee or authorization.

The product specification does not include any authorization for the intellectual property owned by our company or any third party. With respect to the information contained in this product specification, we make no explicit or implied warranties, including but not limited to the accuracy of the specification, its fitness for commercial use, suitability for specific purposes, or non-infringement of our company's or any third party's intellectual property. We also do not assume any responsibility for any incidental or consequential losses related to this specification document and its use.

We do not assume any obligations regarding application assistance or customer product design. Customers are responsible for their own use of our company's products and applications. In order to minimize risks associated with customer products and applications, customers should provide thorough design and operational safety validation.

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Once discovered, the company will pursue its legal responsibility according to law and compensate for all losses caused to the company.

Please note that the product is used within the conditions described in this document, paying particular attention to the absolute maximum rating, operating voltage range, and electrical characteristics. The Company shall not be liable for any damage caused by malfunctions, accidents, etc. caused by the use of the product outside the conditions stated in this document.

Division I has been committed to improving the quality and reliability of products, but all semiconductor products have a certain probability of failure, which may lead to some personal accidents, fire accidents, etc.When designing products, pay full attention to redundancy design and adopt safety indicators, so as to avoid accidents.

When using our chips to produce products, Division I shall not be liable for any patent dispute arising from the use of the chip in the product, the specification of the product, or the country of import, etc., in the event of a patent dispute over the products including the chip.